- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

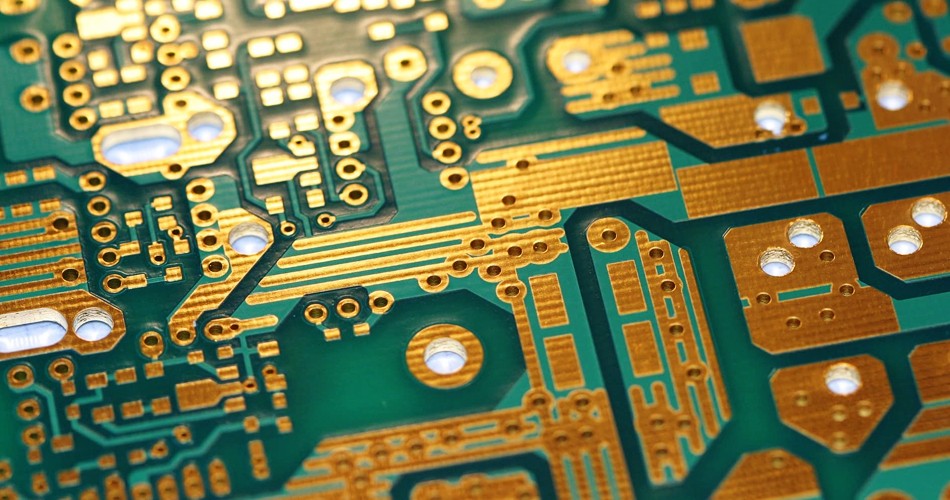

Thiết kế PCB tốc độ cao: Cân nhắc tính toàn vẹn tín hiệu và cặp vi sai

Tính toàn vẹn của tín hiệu và các cặp vi sai là những cân nhắc quan trọng ở tốc độ caothiết kế PCB. Việc duy trì tính toàn vẹn tín hiệu và độ chính xác của cặp vi sai là rất quan trọng đối với hiệu suất của các mạch tốc độ cao. Dưới đây là một số cân nhắc quan trọng cho cả hai khía cạnh:

Cân nhắc tính toàn vẹn tín hiệu:

1. Đặc điểm đường dây truyền tải:

Hiểu các thông số đặc tính của đường truyền, bao gồm trở kháng đặc tính, độ trễ truyền và tốc độ tín hiệu. Điều này giúp đảm bảo tín hiệu không bị suy giảm hoặc biến dạng trong quá trình truyền.

2. Mặt phẳng đất:

Đảm bảo rằng có đủ diện tích mặt đất để cung cấp đường dẫn tín hiệu trở lại tốt. Giảm độ tự cảm và điện trở của đường truyền tín hiệu trở lại.

3. Tiếng ồn nguồn điện:

Thực hiện các biện pháp giảm nhiễu nguồn điện và ghép chéo tín hiệu. Điều này có thể bao gồm việc bổ sung thêm tụ điện tách rời, cuộn cảm giảm nhiễu và bộ lọc giữa nguồn và mặt đất.

4. Tách lớp tín hiệu:

Sử dụng thiết kế PCB nhiều lớp và tách các lớp tín hiệu khác nhau để giảm nhiễu xuyên âm tín hiệu và nhiễu điện từ. Đảm bảo rằng lớp mặt đất cung cấp khả năng che chắn thích hợp giữa các lớp tín hiệu khác nhau.

5. Cặp vi sai và tín hiệu một đầu:

Đối với các tín hiệu vi sai tốc độ cao, hãy sử dụng các đường cặp vi sai để giảm nhiễu xuyên âm và cải thiện khả năng chống nhiễu. Nên tránh các tín hiệu một đầu càng nhiều càng tốt vì chúng dễ bị nhiễu từ bên ngoài hơn.

Cân nhắc cho các cặp vi sai:

1. Thiết kế cặp vi sai:

Các tín hiệu vi sai phải đối xứng và độ dài của hai đường tín hiệu phải khớp nhau để đảm bảo thời gian đến tín hiệu bằng nhau trong quá trình thiết kế PCB.

Hiểu trở kháng đặc tính của cặp vi sai và đảm bảo rằng trở kháng đặc tính của đường truyền tín hiệu phù hợp với cặp vi sai.

2. Ghép tín hiệu vi sai:

Có thể giảm sự ghép nối giữa các tín hiệu vi sai bằng cách giữ chúng cách nhau đủ xa hoặc sử dụng tấm chắn giữa các cặp vi sai.

3. Che chắn cặp vi sai:

Đối với môi trường đặc biệt ồn ào, hãy cân nhắc sử dụng tấm chắn của các cặp vi sai để cải thiện hiệu suất chống nhiễu.

4. Thiết bị đầu cuối và giao diện của cặp vi sai:

Đảm bảo rằng các thiết bị đầu cuối và giao diện của các cặp vi sai được chọn đúng để phù hợp với yêu cầu ứng dụng.

5. Phân tích tính toàn vẹn tín hiệu:

Sử dụng các công cụ phân tích tính toàn vẹn tín hiệu để mô phỏng và phân tích hiệu suất của các tín hiệu vi sai nhằm phát hiện trước các vấn đề tiềm ẩn.

Tóm lại, tính toàn vẹn tín hiệu và cân nhắc cặp vi sai trong thiết kế PCB tốc độ cao là những yếu tố chính để đảm bảo hiệu suất mạch ổn định. Những yếu tố này cần được xem xét cẩn thận trong giai đoạn thiết kế và thực hiện chính xác trong quá trình bố trí và định tuyến. Sử dụng các công cụ kỹ thuật hiện đại và phân tích mô phỏng có thể giúp các kỹ sư hiểu rõ hơn và tối ưu hóa thiết kế bảng mạch tốc độ cao.

Gửi yêu cầu

-

Delivery Service

-

Payment Options